Processadores 6502 e 65C02

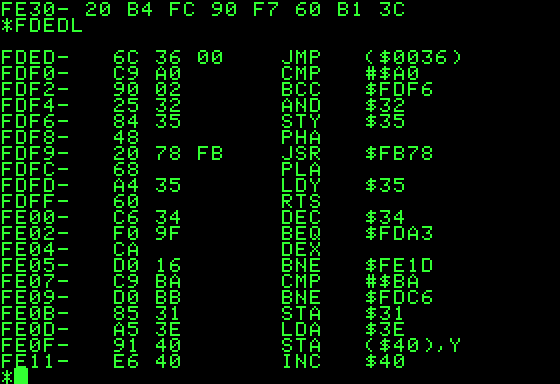

Códigos do assembler 6502/65C02

Apresentando o MOS 6502

O MOS 6502 é um microprocessador de 8 bits projetado por Chuck Peddle para a MOS Technology em 1975.

Quando foi apresentado, era a CPU completa mais barata do mercado, custando cerca de 1/6 (ou menos) do preço de dispositivos similares feitos por grandes empresas concorrentes, como Motorola e Intel.

Era ainda mais rápido do que a maioria deles, e, juntamente com o Zilog Z80, deu origem a uma série de projetos de computadores que eventualmente resultaram na revolução dos computadores domésticos dos anos 1980.

A fabricação do 6502 foi também suprida originalmente pela Rockwell e Synertek, e posteriormente licenciada para várias outras empresas; ele ainda é produzido para uso em sistemas embarcados.

Descrição ténica

A lógica interna do 6502 funciona na mesma velocidade do clock externo, mas apesar das baixas velocidades do clock o desempenho do 6502 era competitivo com outras CPUs contemporâneas que utilizavam clocks com mais velocidade.

Isso se dá devido a máquina de estado simples que é implementada pela lógica computacional (sem relógio). A baixa frequência do clock moderou o requisito de velocidade da memória e periféricos acoplados ao CPU, já que apenas 50% do clico do clock estava disponível para o acesso à memória.

Como o chip só acessava a memória durante algumas partes do ciclo do clock, assim esses ciclos eram indicados pelo pino de baixa PHI clock-out, já outros chips podiam acessar a memória durante os momentos em que o 6502 estava fora do barramento.

Endereçamento

O chip utiliza registradores de índice e pilha efetivamente com vários modos de endereçamento, incluindo um modo rápido de "página direta", que é semelhante ao encontrado no PDP-8, que acessava locais de memória dos endereços de 0 a 255 com um único endereço de 8 bits.

Em alguns microcomputadores baseados em 6502 com um sistema operacional, o sistema operacional usava a maior parte da página direta, deixando apenas alguns locais para o usuário.

Aplicações do MOS 6502

O primeiro dispositivo a utilizar o microprocessador foi o Apple I em 1976, no ano seguinte foi utilizado no Apple II e no Commodore PET, em 1979 na família Atari de 8-bits.

Na década de 1980 foi utilizado no Acorn Atom, BBC Micro, Oric e Commodore VIC-20.

O surgimento do CMOS 65C02

O microprocessador Western Design Center (WDC) 65C02 é uma versão CMOS aprimorada do MOS 6502. O 65C02 corrigiu vários problemas do 6502 original e adicionou algumas novas instruções, mas sua principal característica foi o uso bastante reduzido no consumo de energia, na ordem de 10 a 20 vezes menos do que o 6502 original rodando na mesma velocidade.

O consumo de energia reduzido tornou o 65C02 útil em computadores portáteis e sistemas de microcontroladores em ambientes industriais. Ele tem sido usado em alguns computadores domésticos, bem como em aplicações, incluindo dispositivos implantados de grau médico.

O desenvolvimento do WDC 65C02 começou em 1981 com amostras lançadas no início de 1983. O 65C02 foi lançado oficialmente pouco depois. A WDC licenciou o projeto para Synertek, NCR, GTE e Rockwell Semiconductor.

O principal interesse da Rockwell estava no mercado de embutidos e pediu que vários novos comandos fossem adicionados para ajudar nessa função. Mais tarde, eles foram copiados de volta para a versão de linha de base, quando a WDC adicionou dois novos comandos próprios para criar o W65C02. Mais tarde, a Sanyo também licenciou o design, e a Seiko Epson produziu uma versão modificada chamada de oHuC6280.

As primeiras versões usavam encapsulamento DIP de 40 pinos e estavam disponíveis em versões de 1, 2 e 4 MHz, correspondendo às velocidades das versões nMOS originais. Versões posteriores foram produzidas em pacotes PLCC e QFP, bem como PDIP, e com classificações de velocidade de clock muito mais altas. A versão atual da WDC, o W65C02S-14 tem um núcleo totalmente estático e funciona oficialmente em velocidades de até 14 MHz quando alimentado em 5 volts.

A arquitetura básica do 65C02 é idêntica ao 6502 original e pode ser considerada uma implementação de baixo consumo de energia desse projeto. Operando a 1 MHz, a velocidade mais popular para o 6502 original, o 65C02 requer apenas 20 mW, enquanto o original usa 450 mW, uma redução de mais de vinte vezes. O núcleo otimizado manualmente e o uso de baixa potência destinam-se a tornar o 65C02 adequado para projetos de sistema em chip (SoC) de baixa potência.

Um modelo de descrição de hardware Verilog está disponível para projetar o núcleo W65C02S em um circuito integrado específico de aplicação (ASIC) ou uma matriz de portas programáveis em campo (FPGA). Como é comum na indústria de semicondutores, a WDC oferece um sistema de desenvolvimento, que inclui uma placa de desenvolvimento, um emulador in-circuit (ICE) e um sistema de desenvolvimento de software.

Comparação com o NMOS 6502

Arquitetura básica

Embora o 65C02 possa ser pensado principalmente como um 6502 de baixo consumo, ele também corrige vários bugs encontrados no original e adiciona novas instruções, modos de endereçamento e recursos que podem ajudar o programador a escrever programas menores e de execução mais rápida. Estima-se que o programa em linguagem assembly 6502 médio pode ser feito de 10 a 15 por cento menor no 65C02 e ver uma melhoria semelhante no desempenho, principalmente por meio de acessos à memória evitados pelo uso de menos instruções para realizar uma determinada tarefa.

Instruções não documentadas removidas

O 6502 original tinha 56 instruções, que, quando combinadas com diferentes modos de endereçamento, produziam um total de 151 opcodes dos possíveis 256 padrões de opcode de 8 bits. Os 105 opcodes restantes não utilizados foram indefinidos, com o conjunto de códigos com 4 bits de ordem inferior com 3, 7, B ou F deixados totalmente sem uso, o código com 2 de ordem inferior tendo apenas um único opcode.

O 6502 era famoso pela maneira como alguns desses códigos restantes realmente executavam ações. Devido à forma como o decodificador de instruções do 6502 funcionava, simplesmente definir certos bits no opcode faria com que partes do processamento da instrução ocorressem. Alguns desses opcodes imediatamente travavam o processador, enquanto outros executavam funções úteis e até recebiam mnemônicos de montador não oficiais pelos usuários.

O 65C02 adicionou vários novos opcodes que usaram vários desses slots de "instrução não documentada" anteriormente, por exemplo, $FF agora era usado para a nova instrução BBS (veja abaixo). Aqueles que permaneceram verdadeiramente não utilizados foram configurados para executar NOPs. Programas que tiraram proveito desses códigos não funcionarão no 65C02.

Correções de bugs

O 6502 original tinha várias erratas quando lançado inicialmente. As primeiras versões do processador tinham uma RORinstrução defeituosa (girar para a direita), que emite a tecnologia MOS abordada por não documentar a instrução ROR que foi corrigido logo que foi detectado em produção e não foi um problema para a grande maioria das máquinas que usavam o processador.

Em contraste, um bug notório que está presente em todas as variantes do NMOS 6502 envolve a instrução de salto ao usar endereçamento indireto. Neste modo de endereçamento, o endereço de destino da instrução JMP é buscado na memória, o vetor de salto, em vez de ser um operando para a instrução JMP. Por exemplo, JMP ($1234) buscaria o valor nos locais de memória $1234 (byte menos significativo) e $1235 (byte mais significativo) e carregaria esses valores no contador de programa, o que faria com que o processador continuasse a execução no endereço armazenado no vetor.

O bug aparece quando o endereço do vetor termina em $FF, que é o limite de uma página de memória. Nesse caso, buscará o byte mais significativo do endereço de destino de $00 da página original em vez de $00 da nova página. Portanto, obteria o byte menos significativo do endereço de destino em $12FF e o byte mais significativo do endereço de destino em $1200 em vez de $1300. O 65C02 corrigiu esse problema.

Mais um descuido do que um bug, o estado do sinalizador (D)ecimal no registro de status do NMOS 6502 é indefinido após uma reinicialização ou interrupção. Isso significa que os programadores precisam definir o sinalizador para um valor conhecido para evitar erros relacionados a operações aritméticas. Como resultado, encontra-se uma instrução CLD (CLear Decimal) em quase todos os manipuladores de interrupção do 6502, bem como no início do código de reset. O 65C02 limpa automaticamente este sinalizador depois de empurrar o registrador de status para a pilha em resposta a qualquer interrupção ou em resposta a uma reinicialização de hardware, colocando o processador de volta no modo aritmético binário.

Durante a aritmética do modo decimal, o NMOS 6502 atualizará os sinalizadores (N)egative, o(V)erflow e (Z)ero para refletir o resultado da aritmética binária subjacente, ou seja, os sinalizadores estão refletindo um resultado calculado antes do processador realizando a correção decimal. Em contraste, o 65C02 configura esses sinalizadores de acordo com o resultado da aritmética decimal, ao custo de um ciclo de clock extra por instrução aritmética.

Ao executar uma instrução read-modify-write (R-M-W), como em INC addr, todas as variantes NMOS farão uma escrita dupla em addr, primeiro reescrevendo o valor atual encontrado em addr e depois escrevendo o valor modificado. Esse comportamento pode resultar em bugs difíceis de resolver se addr for um registro de hardware. Isso pode ocorrer se o hardware estiver observando alterações no valor do registrador e então realizar uma ação, neste caso, ele realizará duas ações, uma com o valor original e outra com o novo valor. Em vez disso, o 65C02 executa uma leitura dupla de addr, seguida por uma única gravação.

Ao executar o endereçamento indexado, se a indexação cruzar um limite de página, todas as variantes do NMOS 6502 lerão um endereço inválido antes de acessar o endereço correto. Assim como em uma instrução R-M-W, esse comportamento pode causar problemas ao acessar registradores de hardware via indexação. O 65C02 corrigiu esse problema executando uma leitura fictícia do opcode da instrução quando a indexação cruzava um limite de página. No entanto, essa correção introduziu um novo bug que ocorre quando o endereço base está em um limite de página uniforme (o que significa que a indexação nunca cruzará para a próxima página). Com o novo bug, uma leitura fictícia é executada no endereço base antes da indexação, de modo que LDA $1200,X fará uma leitura fictícia em $1200 antes do valor de X ser adicionado a $1200. Novamente, se indexar em endereços de registro de hardware, esse bug pode resultar em comportamento indefinido.

Se um NMOS 6502 estiver buscando um opcode BRK (interrupção de software) ao mesmo tempo em que ocorre uma interrupção de hardware, o BRK será ignorado conforme o processador reage à interrupção de hardware. O 65C02 lida corretamente com essa situação atendendo a interrupção e executando o BRK.

Novos modos de endereçamento

O 6502 possui dois modos de endereçamento indireto que cancelam a referência por meio de endereços de 16 bits armazenados na página zero:

- Indireta indexada, LDA ($10,X), adiciona o registrador X ao endereço zero da página fornecido antes de ler o vetor de 16 bits. Neste exemplo, se X for 5, ele lê o endereço de 16 bits do local $15/$16. Isso é útil quando há uma matriz de ponteiros na página zero.

- Indireta indexada LDA ($10),Y, adiciona o registrador Y ao vetor de 16 bits lido do endereço zero da página fornecido. Por exemplo, se Y for 5 e $10/$11 contiver o vetor $1000, isso lerá o valor de $1005. Isso executa o endereçamento de deslocamento de ponteiro.

Uma desvantagem desse modelo é que, se a indexação não for necessária, mas o endereço estiver na página zero, um dos registradores de índice ainda deve ser definido como zero e usado em uma dessas instruções. O 65C02 adicionou um modo de endereçamento indireto não indexado LDA ($10) a todas as instruções que usavam modos indexados indiretos e indiretos, liberando os registradores de índice.

A instrução JMP do 6502 tinha um modo de endereçamento exclusivo (entre 6502 instruções) conhecido como "absoluto indireto" que lia um valor de 16 bits de um determinado endereço de memória e depois pulava para o endereço nesse valor de 16 bits. Por exemplo, se o local de memória $A000 contiver $34 e $A001 contiver $12, JMP ($A000) leria esses dois bytes, construiria o valor $1234 e depois pularia para esse local.

Um uso comum para endereçamento indireto é construir tabelas de ramificações, uma lista de pontos de entrada para sub-rotinas que podem ser acessadas usando um índice. Por exemplo, um driver de dispositivo pode listar os pontos de entrada para OPEN, CLOSE, READ, etc em uma tabela em $A000. READ é a terceira entrada, indexada a zero, e cada endereço requer 16 bits, então para chamar um READ usaria algo semelhante a JMP ($A004). Se o driver for atualizado e o código da sub-rotina se mover na memória, qualquer código existente ainda funcionará enquanto a tabela de ponteiros permanecer em $A000.

O 65C02 adicionou o novo modo "indireto absoluto indexado" que facilitou o uso de tabelas de ramais. Este modo adiciona o valor do registrador X ao endereço absoluto e retira o endereço de 16 bits do local resultante. Por exemplo, para acessar a função READ da tabela acima, armazenaríamos 4 em X, depois JMP ($A000,X). Esse estilo de acesso simplifica o acesso às tabelas de ramificação, pois um único endereço de base é usado em conjunto com um deslocamento de 8 bits. O mesmo poderia ser alcançado na versão NMOS usando o modo indireto indexado, mas apenas se a tabela estivesse na página zero, um recurso limitado. Permitir que elas sejam construídas fora da página zero não apenas diminuiu a demanda por esse recurso, mas também permitiu que as tabelas fossem construídas em ROM.

Instruções novas e modificadas

Além dos novos modos de endereçamento, o "modelo base" 65C02 também adicionou um conjunto de novas instruções.

- INC e DEC sem parâmetros agora incrementa ou decrementa o acumulador. Este foi um descuido estranho no conjunto de instruções original, que incluía apenas INX / DEX, INY / DEY e INC addr/ DEC addr. Alguns montadores usam as formas alternativas INA / DEA ou INC A / DEC A.

- STZ addr, STore Zero no endereço. Substitui a necessidade de usar LDA #0;STA addr e não exige a alteração do valor do acumulador. Como essa tarefa é comum na maioria dos programas, o uso do STZ pode reduzir o tamanho do código, tanto eliminando o LDA quanto qualquer código necessário para salvar o valor do acumulador, normalmente um par PHA PLA.

- PHX, PLX, PHY, PLY, empurra e puxa os registradores X e Y para/da pilha. Anteriormente, apenas o acumulador e o registrador de status tinham instruções push e pull. X e Y só podem ser empilhados movendo-os primeiro para o acumulador com TXA ou TYA, alterando assim o conteúdo do acumulador e usando PHA.

- BRA, BRanch Always. Opera como um JMP mas usa um endereço relativo de 1 byte como outros ramos, economizando um byte. A velocidade é geralmente a mesma que o JMP absoluto de 3 ciclos, a menos que uma página seja cruzada, o que tornaria o BRA 1 ciclo mais longo (4 ciclos). Como o endereço é relativo, também é útil ao escrever código relocável, uma tarefa comum na era anterior às unidades de gerenciamento de memória .

Instruções de manipulação de bits

Tanto a WDC quanto a Rockwell contribuíram com melhorias para as funções de teste e manipulação de bits no 65C02. A WDC adicionou novos modos de endereçamento à instrução BIT que estava presente no 6502, bem como duas novas instruções para manipulação conveniente de campos de bits, uma atividade comum em drivers de dispositivo.

O BIT no 65C02 adiciona o modo imediato, página zero indexada por X e indexada absoluta por endereçamento X. O endereçamento de modo imediato é particularmente conveniente por ser completamente não destrutivo. Por exemplo:

LDA $1234

BIT #%00010000

pode ser usado no lugar de:

LDA $1234

AND #%00010000

A operação AND altera o valor no acumulador, de modo que o valor original carregado de $1234 é perdido. O uso BIT deixa o valor no acumulador inalterado, para que o código subsequente possa fazer testes adicionais em relação ao valor original, evitando ter que recarregar o valor da memória.

Além dos aprimoramentos da instrução BIT, a WDC adicionou duas instruções projetadas para manipular convenientemente os campos de bits:

- TSB addr e TRB addr, Test e Set Bit e Test e Reset Bit.

Uma máscara no acumulador ( .A) é logicamente ANDed (adicionado) com memória em addr, cuja localização pode ser página zero ou absoluta. O sinalizador Z no registrador de status é condicionado de acordo com o resultado do AND lógico - nenhum outro sinalizador de registrador de status é afetado. Além disso, os bits em addr são definidos (TSB) ou limpos (TRB) de acordo com a máscara em .A. De forma sucinta, o TSB executa um OR lógico após o AND lógico e armazena o resultado do OR lógico em addr , enquanto o TRB armazena os resultados do AND lógico em addr . Em ambos os casos, o sinalizador Z no registrador de status indica o resultado de antes do conteúdo de .A AND addr. TRB e TSB substituem assim uma sequência de instruções, essencialmente combinando a instrução BIT com etapas adicionais para salvar as alterações computacionais, mas de uma forma que informa o status do valor afetado antes de ser alterado.

As alterações da Rockwell adicionaram mais instruções de manipulação de bits para configurar e testar diretamente qualquer bit e combinar o teste, limpar e ramificar em um único opcode. As novas instruções estavam disponíveis desde o início na família R65C00 da Rockwell, mas não faziam parte da especificação 65C02 original e não eram encontradas em versões feitas pela WDC ou seus outros licenciados. Estes foram posteriormente copiados de volta para o design da linha de base e estavam disponíveis em versões posteriores do WDC.

As instruções específicas da Rockwell são:

- SMBbit# zp / RMBbit# zp. Definir ou Redefinir (limpar) bit número bit# em zero página byte zp.

RMB e SMB são usados para limpar (RMB) ou definir (SMB) bits individuais em um campo de bits, cada um substituindo uma sequência de três instruções. Como RMB e SMB são apenas endereçamento de página zero, essas instruções são limitadas em utilidade e são principalmente de valor em sistemas nos quais os registradores de dispositivo estão presentes em página zero. O componente bit# da instrução geralmente é escrito como parte do mnemônico, como o SMB1 $12 que define o bit 1 no endereço de página zero $12. Alguns montadores tratam o bit# como parte do operando da instrução, por exemplo, SMB 1,$12, que tem a vantagem de permitir que seja substituído por um nome de variável ou número calculado.

- BBR bit#,offset,addr e BBS bit#,offset,addr. Ramificar no Bit Set/Reset.

Mesmo endereçamento de página zero e limitações como RMB e SMB, mas desvia para addr se o bit selecionado estiver limpo (BBR) ou definido (BBS). Como é o caso de RMB e SMB, BBR e BBS substituem uma sequência de três instruções.

Modos de baixo consumo

Além dos novos comandos acima, a WDC também adicionou as instruções STP e WAI para oferecer suporte aos modos de baixo consumo de energia.

STP, STop the Processor, interrompeu todo o processamento até que uma reinicialização de hardware fosse emitida. Isso pode ser usado para colocar um sistema em "suspensão" e, em seguida, acordá-lo rapidamente com uma reinicialização. Normalmente, isso exigiria algum sistema externo para manter a memória principal e não era amplamente utilizado.

WAIt teve um efeito semelhante, entrando no modo de baixo consumo de energia, mas esta instrução acordou o processador novamente na recepção de uma interrupção. Anteriormente, lidar com uma interrupção geralmente envolvia executar um loop para verificar se uma interrupção foi recebida, às vezes conhecida como "looping", verificar o tipo quando uma é recebida e, em seguida, pular para o código de processamento. Isso significava que o processador estava funcionando durante todo o processo, mesmo quando nenhuma interrupção estava ocorrendo.

Em contraste, no 65C02, o código de interrupção pode ser escrito tendo um WAI seguido imediatamente por um JSR ou JMP para o manipulador. Quando o WAI foi encontrado, o processamento parou e o processador entrou no modo de baixo consumo de energia. Quando a interrupção foi recebida, ela imediatamente processou JSR e tratou a solicitação.

Isso tinha a vantagem adicional de melhorar um pouco o desempenho. No caso "looping", a interrupção pode chegar no meio de uma das instruções do loop e, para permitir que ela reinicie após retornar do manipulador, o processador gasta um ciclo para salvar sua localização. Com WAI, o processador entra no estado de baixo consumo de energia em um local conhecido onde todas as instruções são garantidas como completas, de modo que, quando a interrupção chega, ela não pode interromper uma instrução e o processador pode continuar com segurança sem gastar um estado de economia de ciclo.

Características

Lançamento:

- MOS 6502 - 1975

- COS 65C02 - 1983

Velocidade:

- 6502 executando entre 1 Mhz até 3 Mhz

- 65C02 executando entre 1 Mhz até 14 Mhz

BUS de dados:

- 6502: 8 bits

- 65C02: 8 bits

BUS de endereços e contador de programa:

- 6502: 16 bits

- 65C02: 16 bits

Conjunto de Instruções:

- 6502: 56 instruções

- 65C02: 69 instruções

Memória RAM:

- 6502: máximo de 64Kb

- 65C02: máximo de 64Kb

Voltagem:

- 6502: 0,3V até 7V

- 65C02: 1,71V até 5,25V

Guia rápido conjunto de instruções 6502

Instruções por ordem alfabética

Legenda para os Flags:

+ Modificado

- Não modificado

1 Marcado

0 Desmarcado

M6 Bit 6 da memória

M7 Bit 7 da memória

Legenda para os ciclos das instruções:

* adicione 1 ciclo se o limite da página for ultrapassado

** adicione 1 ciclo se ocorrer ramificação na mesma página

adicione 2 ciclos se ocorrer ramificação para página diferente

ADC

Add Memory to Accumulator with Carry

Soma conteúdo da Memória no Acumulador com Carry

Flags afetados após a execução:

N Z C I D V

+ + + - - +

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| imediato | ADC #oper | 69 | 2 | 2 |

| zeropage | ADC oper | 65 | 2 | 3 |

| zeropage,X | ADC oper,X | 75 | 2 | 4 |

| absoluto | ADC oper | 6D | 3 | 4 |

| absoluto,X | ADC oper,X | 7D | 3 | 4* |

| absoluto,Y | ADC oper,Y | 79 | 3 | 4* |

| (indireto,X) | ADC (oper,X) | 61 | 2 | 6 |

| (indireto),Y | ADC (oper),Y | 71 | 2 | 5* |

AND

AND Memory with Accumulator

AND Memory with Accumulator

Executa um AND do conteúdo de Memória com o Acumulador

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | AND #oper | 29 | 2 | 2 |

| zeropage | AND oper | 25 | 2 | 3 |

| zeropage,X | AND oper,X | 35 | 2 | 4 |

| absolute | AND oper | 2D | 3 | 4 |

| absolute,X | AND oper,X | 3D | 3 | 4* |

| absolute,Y | AND oper,Y | 39 | 3 | 4* |

| (indirect,X) | AND (oper,X) | 21 | 2 | 6 |

| (indirect),Y | AND (oper),Y | 31 | 2 | 5* |

ASL

Shift Left One Bit (Memory or Accumulator)

Deslocar (rotaciona) um bit do byte para a esquerda (da memória ou do acumulador)

Flags afetados após a execução:

N Z C I D V

+ + + - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| accumulator | ASL A | 0A | 1 | 2 |

| zeropage | ASL oper | 06 | 2 | 5 |

| zeropage,X | ASL oper,X | 16 | 2 | 6 |

| absolute | ASL oper | 0E | 3 | 6 |

| absolute,X | ASL oper,X | 1E | 3 | 7 |

BCC

Branch on Carry Clear

Desvia execução quando flag Carry for zerado (C = 0)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| relative | BCC oper | 90 | 2 | 2 |

BCS

Branch on Carry Set

Desvia execução quando flag Carry for setado (C = 1)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| relative | BCS oper | B0 | 2 | 2** |

BEQ

Branch on Result Zero

Desvia execução quando flag Zero for setado (Z = 1)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| relative | BEQ oper | F0 | 2 | 2** |

BIT

Test Bits in Memory with Accumulator

Testa conteúdo de Bits na memória com o Acumulador

bits 7 and 6 of operand are transfered to bit 7 and 6 of SR (N,V);

the zero-flag is set to the result of operand AND accumulator.

Flags afetados após a execução:

N Z C I D V

M7+ - - - M6

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| zeropage | BIT oper | 24 | 2 | 3 |

| absolute | BIT oper | 2C | 3 | 4 |

BMI

Branch on Result Minus

Desvia execução quando flag Negative for setado (N = 1)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| relative | BMI oper | 30 | 2 | 2** |

BNE

Branch on Result not Zero

Desvia execução quando flag Zero não for setado (Z = 0)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| relative | BNE oper | D0 | 2 | 2** |

BPL

Branch on Result Plus

Desvia execução quando flag Negativo for zerado (N = 0)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| relative | BPL oper | 10 | 2 | 2** |

BRK

Force Break

Força parada de execução

BRK inicia uma interrupção de software semelhante a uma

interrupção de hardware (IRQ). O endereço de retorno colocado na pilha é

PC+2, fornecendo um byte extra de espaço para uma marca de quebra

(identificando o motivo da quebra).

O registrador de status será colocado na pilha com o

sinalizador de quebra definido como 1. No entanto, quando recuperado durante RTI ou por uma

instrução PLP, o flag break será ignorado.

O sinalizador de desativação de interrupção não é definido automaticamente.

Flags afetados após a execução:

N Z C I D V

- - - 1 - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | BRK | 00 | 1 | 7 |

BVC

Branch on Overflow Clear

Desvia execução quando flag Overflow for zerado (V = 0)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| relative | BVC oper | 50 | 2 | 2** |

BVS

Branch on Overflow Set

Desvia execução quando flag Overflow for setado (V = 1)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| relative | BVS oper | 70 | 2 | 2** |

CLC

Clear Carry Flag

Limpa flag Carry

Flags afetados após a execução:

N Z C I D V

- - 0 - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | CLC | 18 | 1 | 2 |

CLD

Clear Decimal Mode

Limpa flag de modo Decimal

Flags afetados após a execução:

N Z C I D V

- - - - 0 -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | CLD | D8 | 1 | 2 |

CLI

Clear Interrupt Disable Bit

Limpa flag de Interrupção

Flags afetados após a execução:

N Z C I D V

- - - 0 - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | CLI | 58 | 1 | 2 |

CLV

Clear Overflow Flag

Limpa flag de Overflow

Flags afetados após a execução:

N Z C I D V

- - - - - 0

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | CLV | B8 | 1 | 2 |

CMP

Compare Memory with Accumulator

Compara byte na Memória com Acumulador

Flags afetados após a execução:

N Z C I D V

+ + + - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | CMP #oper | C9 | 2 | 2 |

| zeropage | CMP oper | C5 | 2 | 3 |

| zeropage,X | CMP oper,X | D5 | 2 | 4 |

| absolute | CMP oper | CD | 3 | 4 |

| absolute,X | CMP oper,X | DD | 3 | 4* |

| absolute,Y | CMP oper,Y | D9 | 3 | 4* |

| (indirect,X | CMP (oper,X) | C1 | 2 | 6 |

| (indirect),Y | CMP (oper),Y | D1 | 2 | 5* |

CPX

Compare Memory and Index X

Compara byte na Memória com Index X

Flags afetados após a execução:

N Z C I D V

+ + + - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | CPX #oper | E0 | 2 | 2 |

| zeropage | CPX oper | E4 | 2 | 3 |

| absolute | CPX oper | EC | 3 | 4 |

CPY

Compare Memory and Index Y

Compara byte na Memória com Index Y

Flags afetados após a execução:

N Z C I D V

+ + + - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | CPY #oper | C0 | 2 | 2 |

| zeropage | CPY oper | C4 | 2 | 3 |

| absolute | CPY oper | CC | 3 | 4 |

DEC

Decrement Memory by One

Decrementa byte na memória com 1

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| zeropage | DEC oper | C6 | 2 | 5 |

| zeropage,X | DEC oper,X | D6 | 2 | 6 |

| absolute | DEC oper | CE | 3 | 6 |

| absolute,X | DEC oper,X | DE | 3 | 7 |

DEX

Decrement Index X by One

Decrementa Index X com 1

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | DEX | CA | 1 | 2 |

DEY

Decrement Index Y by One

Decrementa Index Y com 1

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | DEY o | 88 | 1 | 2 |

EOR

Exclusive-OR Memory with Accumulator

Executa um Exclusive-OR num byte da Memory com o Accumulator

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | EOR #oper | 49 | 2 | 2 |

| zeropage | EOR oper | 45 | 2 | 3 |

| zeropage,X | EOR oper,X | 55 | 2 | 4 |

| absolute | EOR oper | 4D | 3 | 4 |

| absolute,X | EOR oper,X | 5D | 3 | 4* |

| absolute,Y | EOR oper,Y | 59 | 3 | 4* |

| (indirect,X) | EOR (oper,X) | 41 | 2 | 6 |

| (indirect),Y | EOR (oper),Y | 51 | 2 | 5* |

INC

Increment Memory by One

Incrementa byte na Memória com 1

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| zeropage | INC oper | E6 | 2 | 5 |

| zeropage,X | INC oper,X | F6 | 2 | 6 |

| absolute | INC oper | EE | 3 | 6 |

| absolute,X | INC oper,X | FE | 3 | 7 |

INX

Increment Index X by One

Incrementa Index X com 1

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | INX | E8 | 1 | 2 |

INY

Increment Index Y by One

Incrementa Index Y com 1

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | INY | C8 | 1 | 2 |

JMP

Jump to New Location

Desvia a execução para novo endereço de memória

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| absolute | JMP oper | 4C | 3 | 3 |

| indirect | JMP (oper) | 6C | 3 | 5 |

JSR

Jump to New Location Saving Return Address

Desvia a execução para novo endereço de memória (subrotina) e retorna a execução após o desvio

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| absolute | JSR oper | 20 | 3 | 6 |

LDA

Load Accumulator with Memory

Carrega Acumulador com byte da Memória

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | LDA #oper | A9 | 2 | 2 |

| zeropage | LDA oper | A5 | 2 | 3 |

| zeropage,X | LDA oper,X | B5 | 2 | 4 |

| absolute | LDA oper | AD | 3 | 4 |

| absolute,X | LDA oper,X | BD | 3 | 4* |

| absolute,Y | LDA oper,Y | B9 | 3 | 4* |

| (indirect,X) | LDA (oper,X) | A1 | 2 | 6 |

| (indirect),Y | LDA (oper),Y | B1 | 2 | 5* |

LDX

Load Index X with Memory

Carrega Index X com byte da Memória

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | LDX #oper | A2 | 2 | 2 |

| zeropage | LDX oper | A6 | 2 | 3 |

| zeropage,Y | LDX oper,Y | B6 | 2 | 4 |

| absolute | LDX oper | AE | 3 | 4 |

| absolute,Y | LDX oper,Y | BE | 3 | 4* |

LDY

Load Index Y with Memory

Carrega Index Y com byte da Memória

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | LDY #oper | A0 | 2 | 2 |

| zeropage | LDY oper | A4 | 2 | 3 |

| zeropage,X | LDY oper,X | B4 | 2 | 4 |

| absolute | LDY oper | AC | 3 | 4 |

| absolute,X | LDY oper,X | BC | 3 | 4* |

LSR

Shift One Bit Right (Memory or Accumulator)

Deslocar (rotaciona) um bit do byte para a direita (da memória ou do acumulador)

Flags afetados após a execução:

N Z C I D V

0 + + - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| accumulator | LSR A | 4A | 1 | 2 |

| zeropage | LSR oper | 46 | 2 | 5 |

| zeropage,X | LSR oper,X | 56 | 2 | 6 |

| absolute | LSR oper | 4E | 3 | 6 |

| absolute,X | LSR oper,X | 5E | 3 | 7 |

NOP

No Operation

Sem operação (não faz nada na execução)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | NOP | EA | 1 | 2 |

ORA

OR Memory with Accumulator

Executa um OR entre byte na Memória com o Acumulador

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| immediate | ORA #oper | 09 | 2 | 2 |

| zeropage | ORA oper | 05 | 2 | 3 |

| zeropage,X | ORA oper,X | 15 | 2 | 4 |

| absolute | ORA oper | 0D | 3 | 4 |

| absolute,X | ORA oper,X | 1D | 3 | 4* |

| absolute,Y | ORA oper,Y | 19 | 3 | 4* |

| (indirect,X) | ORA (oper,X) | 01 | 2 | 6 |

| (indirect),Y | ORA (oper),Y | 11 | 2 | 5* |

PHA

Push Accumulator on Stack

Coloca o valor do Acumulador na Pilha

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | PHA | 48 | 1 | 3 |

PHP

Push Processor Status on Stack

Coloca registrador de Status do Processador na Pilha

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | PHP | 08 | 1 | 3 |

PLA

Pull Accumulator from Stack

Retorna o valor da Pilha no Acumulador

Flags afetados após a execução:

N Z C I D V

+ + - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | PLA | 68 | 1 | 4 |

PLP

Pull Processor Status from Stack

Retorna o registrador de Status do Processador da Pilha

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | PLP | 28 | 1 | 4 |

ROL

Rotate One Bit Left (Memory or Accumulator)

Gira um Bit do byte para a Esquerda (memória ou acumulador)

Flags afetados após a execução:

N Z C I D V

+ + + - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| accumulator | ROL A | 2A | 1 | 2 |

| zeropage | ROL oper | 26 | 2 | 5 |

| zeropage,X | ROL oper,X | 36 | 2 | 6 |

| absolute | ROL oper | 2E | 3 | 6 |

| absolute,X | ROL oper,X | 3E | 3 | 7 |

|

ROR

Rotate One Bit Right (Memory or Accumulator)

Gira um Bit do byte para a Direita (memória ou acumulador)

Flags afetados após a execução:

N Z C I D V

+ + + - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| accumulator | ROR A | 6A | 1 | 2 |

|

| zeropage | ROR oper | 66 | 2 | 5 |

|

| zeropage,X | ROR oper,X | 76 | 2 | 6 |

|

| absolute | ROR oper | 6E | 3 | 6 |

|

| absolute,X | ROR oper,X | 7E | 3 | 7 |

|

RTI

Return from Interrupt

Retona execução após uma Interrupção

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | RTI | 40 | 1 | 6 |

RTS

Return from Subroutine

Retorna a execução para o endereço que desviou a execução (subrotina)

Flags afetados após a execução:

N Z C I D V

- - - - - -

| Endereçamento | Comando | Código | Bytes | Ciclos |

|---|

| implied | RTS | 60 | 1 | 6 |

SBC

Subtract Memory from Accumulator with Borrow

Subtrair memória do acumulador com empréstimo

Flags afetados após a execução:

N Z C I D V

+ + + - - +